Abstract—We report on a GaN power HEMT with a breakdown voltage exceeding 800 V, grown by MBE on sapphire. The high breakdown voltage, surpassing 800 V, is achieved through the use of an ultra-thin AlN buffer layer grown by MBE and the implementation of a single-level gate field plate technique. The MBE technique facilitates the growth of a dopant-free buffer layer and pseudomorphic epilayers, which is advantageous for the high reliability of GaN power HEMTs. Additionally, the single-level gate field plate technique aids in reducing the overall fabrication cost and also enhances the reliability of GaN power HEMTs. These merits highlight the potential of the reported GaN power HEMT for applications in high-power electronics.

Keywords: GaN HEMTs, MBE, field plate, breakdown

I. INTRODUCTION

With the continuous development of power electronic technology, gallium nitride (GaN) power devices have emerged as a new generation of high-performance semiconductor devices. GaN high electron mobility transistors (HEMTs) grown by metal organic chemical vapor deposition (MOCVD) have achieved success in commercial applications of high-power switch devices, including power adapters, electric vehicle charging piles, and communication base station power supplies [1]. Here, we employ the molecular beam epitaxy (MBE) technique to grow GaN HEMTs on sapphire. MBE offers several advantages: firstly, it allows for precise control over the growth rate and thickness of the GaN and related layers with atomic-level precision. This enables the fabrication of high-quality heterojunctions, which are crucial for the excellent performance of GaN HEMTs. Secondly, the GaN growth process in MBE is carried out under ultra-high vacuum conditions, minimizing the incorporation of impurities and defects [2]. This results in enhanced electron mobility and carrier confinement within the two-dimensional electron gas (2DEG) region of GaN HEMTs. Moreover, the ability to grow insulating buffer layers without doping in the materials helps in avoiding trap-induced phenomena such as the current collapse effect and also leads to higher reliability due to the absence of trap-related leakage mechanisms. [3].

Additionally, we employ a single-level gate field plate technique to optimize the electric field distribution and achieve a high breakdown voltage of over 800 V. This technique, being the simplest form of field plate, helps to decrease the overall fabrication cost and enhance reliability when compared to multi-level field plates. Moreover, transitioning from a single-level to a multi-level field plate can yield even higher breakdown voltages, fulfilling the requirements for applications in electric vehicles and industrial power supplies.

II. EXPERIMENT

A. MBE growth

We utilized plasma-assisted MBE equipment to fabricate a complete HEMT structure on a sapphire substrate (Fig. 1 (a)). Initially, a 1 µm AlN buffer layer was deposited onto the sapphire substrate [4]. Subsequently, AlGaN layers with Al compositions of 70%, 50% and 20% were grown. Following this, a 1nm AlN spacer, a GaN channel layer, and a 24 nm 30% AlGaN barrier layer were grown on top of the AlGaN grading layer. Finally, a 10 nm in-situ SiN layer was deposited as a passivation layer.

Fig.1 Schematic (a) epitaxy structure grown by MBE and (b) cross section of GaN power HEMT

B. GaN HEMT fabrication

The schematic cross section of a GaN power HEMT is shown in Fig. 1 (b). Device mesa isolation was performed using inductively coupled plasma reactive ion etching (ICP-RIE) to etch the GaN epilayers to a depth of ~600 nm. With this isolation, the active regions of different devices were isolated by cutting off the 2DEG outside these regions.

Source/drain ohmic contacts with a typical contact resistance of 1.2 Ω·mm were achieved using Ti/Al/Ni/Au (20/120/30/50 nm) deposited by e-beam evaporation and rapid thermal annealing at 800 °C in N2 for 30 seconds. Subsequently, 150 nm SiN was deposited onto the wafer using inductively coupled plasma chemical vapor deposition (ICP-CVD). The gate window (GS) was opened in the 150 nm SiN layer, with a recess depth of ~120 nm, leaving ~30 nm of SiN as the gate insulator. Ti/Al/Ti (30/500/30 nm) was deposited to serve as the gate field plate metal (GT). The gate GS and the gate field plate metal GT together formed a single-level gate field plate structure to achieve a high breakdown voltage. Following this, 1 µm SiN was deposited by ICP-CVD, and via holes (V0) were created using ICP-RIE. Interconnection M1 to the source/drain ohmic contacts was established using Ti/Al/Ti (30/1000/30 nm) through the via holes V0. Finally, 2 µm SiN was deposited by ICP-CVD as the top passivation layer. The fabricated GaN HEMT features a gate length (Lg) of ~2 µm, a gate field plate length of ~9 µm, a gate width of ~100 µm, a gate-source spacing (Lgs) of ~3.5 µm, and a gate-drain spacing (Lgd) of ~22 µm.

III. RESULTS AND DISCUSSION

The characterization of device mesa isolation was conducted on two mesa isolation squares with a separation of ~10 µm and widths of ~100 µm. Fig. 2 illustrates the mesa isolation characteristics with a two-terminal bias ranging from 0 to 1100 V. The leakage current is <2×10⁻⁷ A, demonstrating the excellent insulating properties of the 1 µm thin AlN buffer layer grown on sapphire using MBE. Such superior insulating behavior is essential for ensuring sufficiently high breakdown voltages. Figs. 3 and 4 depict the typical DC output and transfer characteristics of the fabricated GaN HEMTs.

Fig. 2 Mesa isolation characteristics of GaN power HEMT grown by MBE

Fig. 3 Output characteristics of GaN power HEMT grown by MBE

Fig. 4 Transfer characteristics of GaN power HEMT grown by MBE

The GaN HEMT demonstrates an on-state current of ~160 mA/mm and an ON-resistance of 45 Ω·mm at a drain bias (Vds) of 10 V and a gate bias (Vgs) of 0 V, as depicted in Fig. 3. The threshold voltage (Vth), determined using the linear extrapolation method (i.e., the gate bias intercept of the linear extrapolation of the drain current at the peak transconductance point), is extracted to be approximately -12.5 V for the GaN HEMTs. The device exhibits an ON/OFF current ratio of approximately 6×10⁴ and a low gate leakage current below 1 µA/mm at a drain bias (Vds) of 5 V, as shown in Fig. 4. The in-situ SiN grown by MBE suppresses interfacial defects, thereby enabling low gate leakage and device operation [5]. The relatively high ON-resistance is attributed to the thin GaN channel and a back barrier composed of 20% AlGaN. Increasing the channel thickness and barrier composition, along with further optimization of the growth process, will lead to a reduction in ON-resistance [6].

The gate and source electrodes are biased at -30 V and 0 V, respectively, with the substrate grounded. The off-state characteristics are depicted in Fig. 5. A leakage current of less than 10 µA/mm is achieved at a gate-drain voltage of 800 V, indicating a breakdown voltage greater than 800 V. During the off-state leakage measurement, the gate current is 1.9 µA/mm, suggesting that the leakage current primarily originates from the source injection current at a drain bias Vds up to 800 V.

The single-level field plate structure implemented here effectively achieves a breakdown voltage greater than 800 V using the simplest form of field plate. This approach helps to reduce the total fabrication cost while maintaining a high breakdown voltage [7].

Fig. 5 Breakdown properties of GaN power HEMT grown by MBE

IV. CONCLUSION

A GaN power HEMT with a breakdown voltage greater than 800 V, grown by MBE on sapphire, has been reported. A breakdown voltage exceeding 800 V was achieved by employing an ultra-thin AlN buffer layer grown by MBE and utilizing a single-level gate field plate technique. The MBE growth process facilitates the creation of a dopant-free AlN buffer layer, which enhances the high reliability of the GaN power HEMT. The single-level gate field plate technique leads to decreased fabrication costs and potentially improves the reliability of the GaN power HEMT. These advantages demonstrate the potential of the fabricated GaN HEMT for applications in high-power electronics at a low cost. Future work will focus on reducing dislocations to demonstrate the breakdown properties of large devices and to decrease ON-resistance by optimizing the compositions of the back barrier and top barrier, as well as the channel thickness.

REFERENCES

[1] Zhibo Cheng, Xiangdong Li, Long Chen, Lezhi Wang, Zilan Li, and Xi Tang, “Achieving ≥ 1200-V high-performance GaN HEMTs on sapphire with carbon-doped buffer,” IEEE Transactions on Electron Devices, vol. 71, pp. 7689-7695, Dec. 2024.

[2] T.D Moustakas, E Iliopoulos, A.V Sampath, H.M Ng, D Doppalapudi, M Misra, D Korakakis, R Singh, “Growth and device applications of III-nitrides by MBE,” Journal of Crystal Growth, vol. 227–228, pp 13-20, Jul. 2001.

[3] E. V. Lutsenko, M. V. Rzheutski, A. G. Vainilovich, I. E. Svitsiankou, V. A. Shulenkova, E. V. Muravitskaya, A. N. Alexeev, S. I. Petrov, and G. P. Yablonskii, “MBE AlGaN/GaN HEMT Heterostructures with optimized AlN buffer on Al2O3,” Semiconductors, vol. 52, pp. 2107–2110, Feb. 2019.

[4] Junbo Wang, Xiangdong Li, Zhibo Cheng, Tao Zhang, Wenyong Zhou, and Long Chen, “Suppressing the leakage of GaN HEMTs on single-crystalline AlN templates by buffer optimization,” in IEEE Transactions on Electron Devices, vol. 71, pp. 6609-6615, Nov. 2024.

[5] Zhikai Tang, Qimeng Jiang, Yunyou Lu, Sen Huang, Shu Yang, Xi Tang, and Kevin J. Chen, “600-V normally off SiNx /AlGaN/GaN MIS-HEMT with large gate swing and low current collapse,” IEEE Electron Device Letters, vol. 34, pp. 1373-1375, Nov. 2013.

[6] Kathia Harrouche, Srisaran Venkatachalam, François Grandpierre, Etienne Okada and Farid Medjdoub, “Impact of undoped channel thickness and carbon concentration on AlN/GaN-on-SiC HEMT performances,” Applied Physics Express, vol. 15, pp 116504, Nov. 2022.

[7] Xiangdong Li et al., “Demonstration of >8-kV GaN HEMTs with CMOS-compatible manufacturing on 6-in sapphire substrates for medium-voltage applications,” IEEE Transactions on Electron Devices, vol. 71, pp. 3989-3993, Jun. 2024.

[1] Zhibo Cheng, Xiangdong Li, Long Chen, Lezhi Wang, Zilan Li, and Xi Tang, “Achieving ≥ 1200-V high-performance GaN HEMTs on sapphire with carbon-doped buffer,” IEEE Transactions on Electron Devices, vol. 71, pp. 7689-7695, Dec. 2024.

[2] T.D Moustakas, E Iliopoulos, A.V Sampath, H.M Ng, D Doppalapudi, M Misra, D Korakakis, R Singh, “Growth and device applications of III-nitrides by MBE,” Journal of Crystal Growth, vol. 227–228, pp 13-20, Jul. 2001.

[3] E. V. Lutsenko, M. V. Rzheutski, A. G. Vainilovich, I. E. Svitsiankou, V. A. Shulenkova, E. V. Muravitskaya, A. N. Alexeev, S. I. Petrov, and G. P. Yablonskii, “MBE AlGaN/GaN HEMT Heterostructures with optimized AlN buffer on Al2O3,” Semiconductors, vol. 52, pp. 2107–2110, Feb. 2019.

[4] Junbo Wang, Xiangdong Li, Zhibo Cheng, Tao Zhang, Wenyong Zhou, and Long Chen, “Suppressing the leakage of GaN HEMTs on single-crystalline AlN templates by buffer optimization,” in IEEE Transactions on Electron Devices, vol. 71, pp. 6609-6615, Nov. 2024.

[5] Zhikai Tang, Qimeng Jiang, Yunyou Lu, Sen Huang, Shu Yang, Xi Tang, and Kevin J. Chen, “600-V normally off SiNx /AlGaN/GaN MIS-HEMT with large gate swing and low current collapse,” IEEE Electron Device Letters, vol. 34, pp. 1373-1375, Nov. 2013.

[6] Kathia Harrouche, Srisaran Venkatachalam, François Grandpierre, Etienne Okada and Farid Medjdoub, “Impact of undoped channel thickness and carbon concentration on AlN/GaN-on-SiC HEMT performances,” Applied Physics Express, vol. 15, pp 116504, Nov. 2022.

[7] Xiangdong Li et al., “Demonstration of >8-kV GaN HEMTs with CMOS-compatible manufacturing on 6-in sapphire substrates for medium-voltage applications,” IEEE Transactions on Electron Devices, vol. 71, pp. 3989-3993, Jun. 2024.

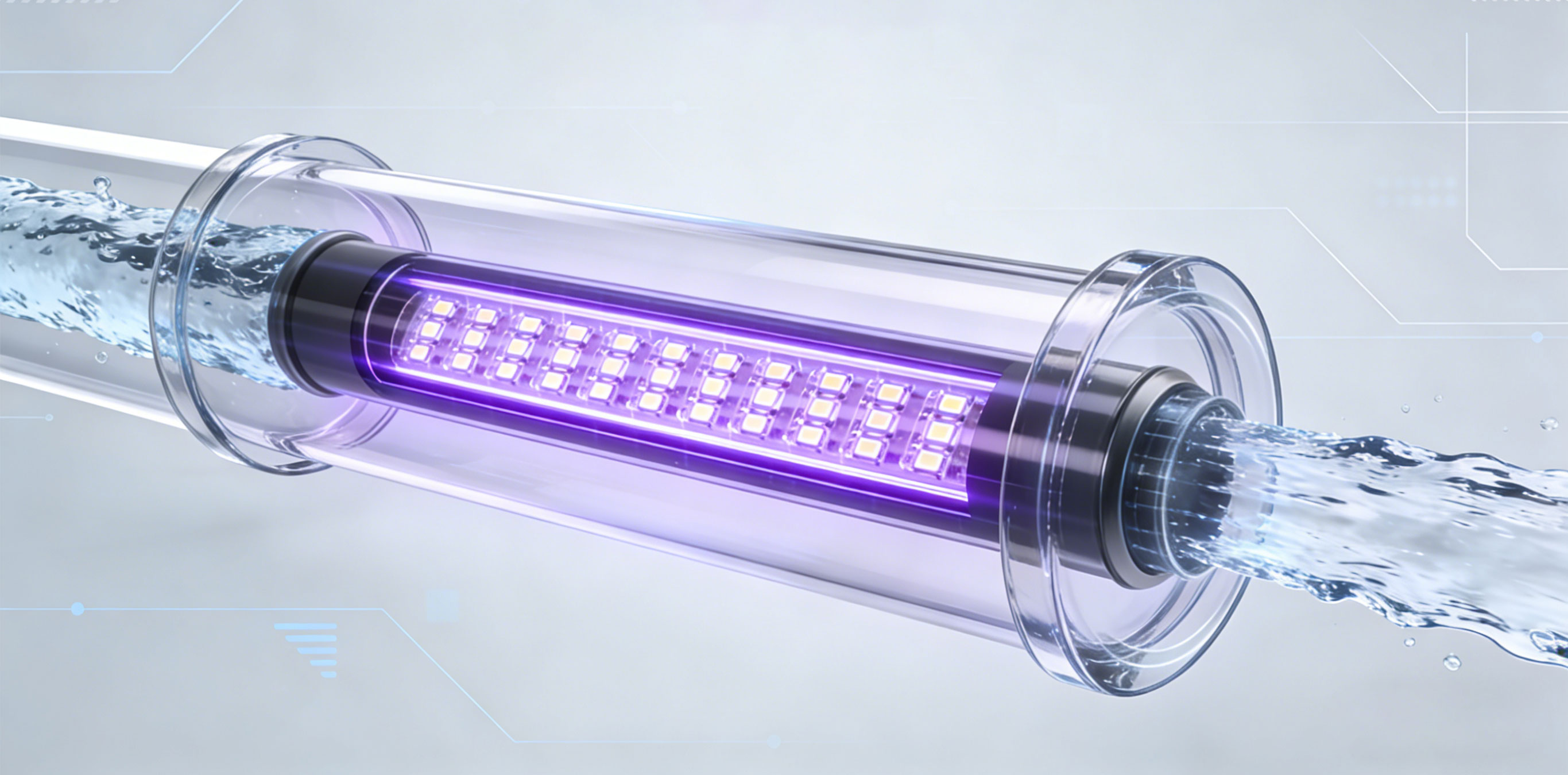

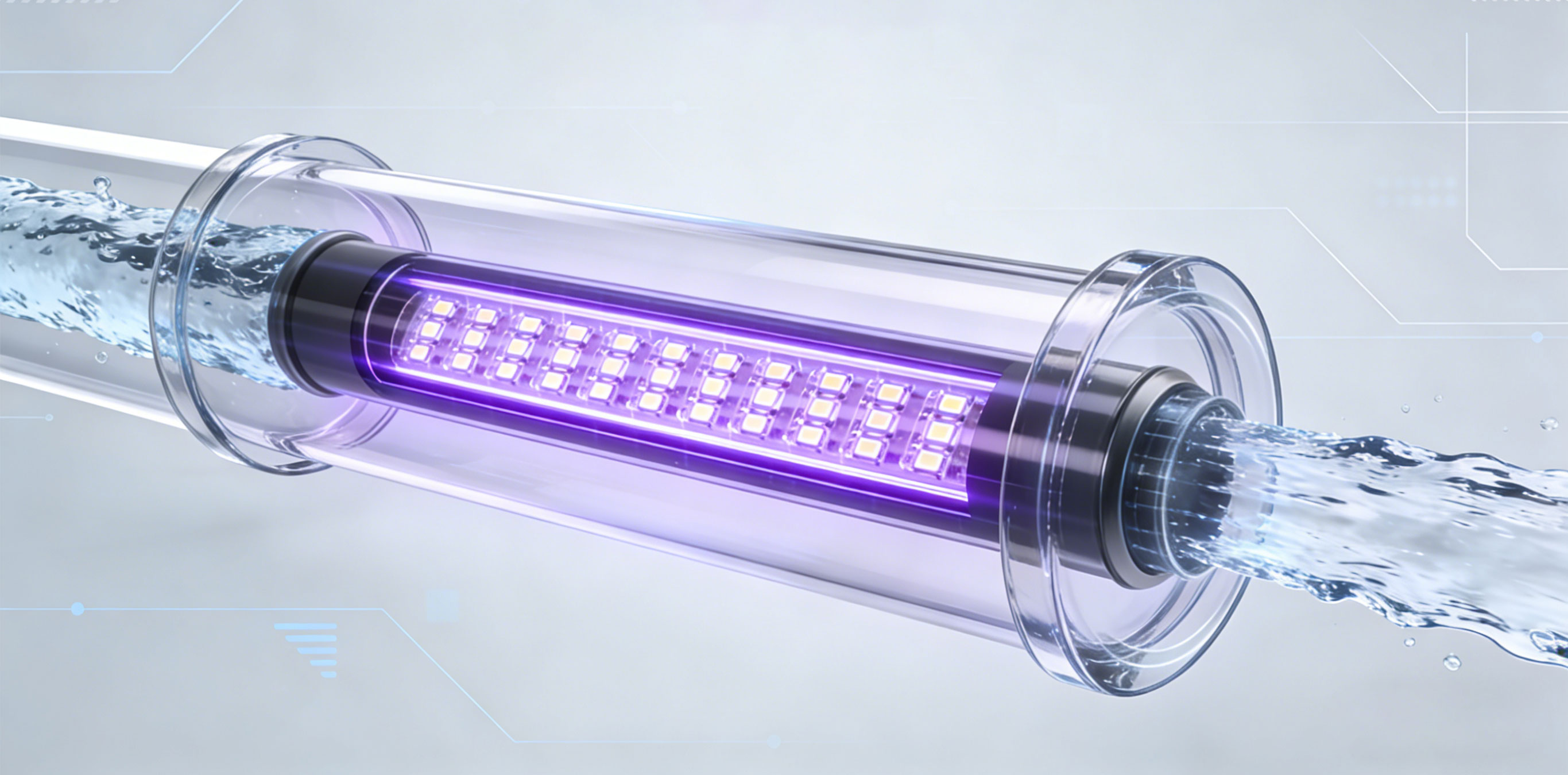

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers.

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers. Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit

Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment.

UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment. UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.

UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.