GaN power high electron mobility transistors (HEMTs) with a breakdown voltage (BV) exceeding 2500 V at/ DSS leakage of 1 μA mm-1 grown by plasma-assisted MBE (PA-MBE) on sapphire was demonstrated with a single field plate structure. Subdividing the 70 nm GaN channel into 12 layers has been shown to exhibit fewer defect states and reduced pore defects, thereby benefiting the BV. The single gate field plate technique helps to simplify the peak electric field condition and also contributes to the high BV. These advantages underscore the potential of the PA-MBE-grown GaN power HEMT for high-power electronic applications. © 2025 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

As power electronic technology continues to evolve, gallium nitride (GaN) power devices have emerged as a new generation of high-performance semiconductor devices.GaN high electron mobility transistors (HEMTs), grown using metal organic CVD (MOCVD), have obtained success in commercial applications as high-power switch devices, including power adapters, electric vehicle charging stations, and communication base station power supplies.1–5) PA-MBE has been widely utilized to grow GaN-based epitaxial structures for RF applications, achieving record frequencies that enter the THz regime.6,7) It has also demonstrated that PA-MBE-grown GaN HEMTs can operate at relatively lower frequencies but with higher breakdown strength or superior linearity.8–10) However, there are few reports on PA-MBE-grown GaN HEMTs for high-power electronic applications. Here, we employ a PA-MBE technique to grow GaN power HEMT structures on sapphire. Compared to MOCVD, PA-MBE can achieve an insulating buffer without the need for doping and enable linear grading for the strain relief layer. A dopant-free buffer is advanta-geous for eliminating current collapse when switching GaN power HEMTs between on and off states, and is therefore crucial for high-frequency performance. Meanwhile, the growth of PA-MBE is carried out under ultra-high vacuum conditions, suppressing the incorporation of background impurities and defects.11) These may also lead to higher reliability. Additionally, we utilize a single gate field plate technique to optimize the electric field distribution and achieve a high breakdown voltage (BV) exceeding 2500 V. The single field plate structure simplifies the peak electric field compared to a multiple field plate structure, and thus can achieve a higher BV.12,13) This technique, being the simplest form of field plate, aids in reducing the overall fabrication cost and enhancing reliability compared to multi-level field plates.

In this work, we implemented a novel growth scheme that involved dividing the 70 nm GaN channel into 12 layers with Ga droplet depletion treatment, in contrast to what was applied in our previous work,12) where a commercially available 300 nm GaN channel was used without such a technique. GaN HEMTs with a BV exceeding 2500 V at a leakage current density IDSS of 1 μA mm−1, grown by PA-MBE on sapphire using a single field plate structure was demonstrated. By subdividing the 70 nm GaN into 12 layers, the quality of the GaN channel is enhanced, resulting in fewer defect states and a lower pore defect density, which in turn benefits the BV. In comparison to previous work on MOCVD,5) our work demonstrates the feasibility of PA-MBE in achieving high BV by applying a novel growth method and paving the way for low-temperature PA-MBE in applications in high-power electronics.

We epitaxially grew two GaN HEMTs, wafer A and B, on sapphire substrates using PA-MBE, as shown in Figs. 1(a) and 1(b). During the growth process, a 1000 nm AlN buffer layer was deposited on a 3-inch sapphire substrate with a (0001) crystal structure and a C-axis orientation that was biased by 2 degrees. This was done at a substrate temperature of 920 °C and a growth rate of 4.5 nm min−1. Without an AlGaN transition layer, the GaN channel was directly grown on the AlN substrate.14) To ensure optimal electrical proper-ties through metallic polarity and atomic-level interlayer bonding, the 70 nm GaN layer was divided into 12of 5.83 nm segments for growth (growth temperature 815 °C, growth rate 1.35 nm min−1) for wafer B. Subsequently, two mole-cular layers of AlN and a 28 nm 22% AlGaN barrier layer were deposited at the same temperature. Finally, the entire epitaxial wafer was passivated with 10 nm SiN through in situ deposition.

Fig. 1. (a) and (b) schematic of the cross-section of epitaxial structures for wafer A and B, (c) and (d) atomic force microscope (AFM) image of the surface of the epitaxial structures for wafer A and wafer B and schematic of (e) the cross-section of and (f) scanning electron microscope (SEM) image of the fabricated GaN HEMT with a single field plate.

The schematic cross-section of a GaN power HEMT is depicted in Fig. 1(e). Device fabrication commenced with the application of a 30 nm SiN passivation layer using low-pressure chemical vapor deposition (LPCVD). Following this, mesa isolation was achieved through N implantation. This process ensures that the active regions of different devices are separated by cutting off the 2DEG outside these areas.15) Source/drain ohmic contacts were realized using Ti/Al/Ni/Au (30/150/50/50 nm) deposited by e-beam eva-poration and rapid thermal annealing at 850 °C in N2 for 60 s.16) Subsequently, a 150 nm layer of SiN was deposited onto the wafer using inductively coupled plasma CVD (ICP-CVD). The gate window was opened in the 150 nm SiN layer, with a recess depth of approximately 120 nm, leaving about 30 nm of SiN as the gate insulator. Ti/Al/Ti (30/500/ 30 nm) was deposited to form the gate metal and the field

plate metal simultaneously. Following this, a 1 μm layer of SiN was deposited by ICP-CVD, and via holes V0 were created using ICP-RIE. Interconnection M1 to the source/drain ohmic contacts was established using Ti/Al/Ti (30/ 1000/30 nm) through the via holes V0. A 2 μm layer of SiN was deposited by ICP-CVD, and via holes V1 were created using ICP-RIE. Interconnection M2 to the source/drain ohmic contacts was established using Ti/Al/Ti (30/2000/30 nm) through the via holes V1. Finally, a 2 μm layer of SiN was deposited by ICP-CVD as the top passivation layer. The fabricated GaN HEMT features a gate length (LG) of ~2 μm, a gate field plate length (LFP) of ∼9 μm, a gate width (WG) of ∼100 μm, a gate-source spacing (LGS) of ∼3.5 μm, and a gate-drain spacing (LGD) of ∼22 μm.

From the transmission line method (TLM), the contact resistance and sheet resistance of the wafer was measured to be 3.6 Ω·mm and 491 Ω sq−1, respectively. From the Hall measurement, the two-dimensional electron gas (2DEG) density NS, field-effect mobility μFE, and the resulting sheet resistance RS are 1.07 × 1013 cm−2, 884 cm2 V−1·s−1, and 660 Ω sq−1, respectively. The relatively high ohmic contact resistance was due to the large contact resistance of the alloyed metal to the low mobility 2DEG.17) The discrepancy between the sheet resistance obtained from TLM measure-ments and that from Hall measurements may indicate that the buffer layer underlying the GaN channel is not sufficiently insulating, leading to parasitic conduction. Further opti-mizing the growth condition of the buffer layer would reduce the sheet resistance as well as enable a thicker channel layer.14)

The characterization of device mesa isolation was con-ducted on two mesa isolation squares with a separation of ~10 μm and widths of about 100 μm. Figure 2 illustrates the mesa isolation characteristics with a two-terminal bias ranging from 0 to 1100 V. The leakage current is less than <1 μA mm−1 and remains almost constant from 0 to 1100 V, implying the good insulating properties of the 1 μm thin AlN buffer layer grown on sapphire using PA-MBE Such insulating behavior is essential for ensuring the pinch-off of the device and sufficiently high BV.

Figures 3 and 4 illustrate the typical output and transfer characteristics of the fabricated GaN HEMTs. Wafer A exhibits an on-state current of ∼290 mA mm−1 at a drain bias (VDS) of 20 V and a gate bias (VGS) of 0 V, with an ON-resistance (Ron) of 35 Ω·mm, as shown in Fig. 3(a). Wafer B displays a comparable Ron but with current saturation in the output characteristics, attributed to the superior channel quality of its subdivided layers. As depicted in Fig. 1(d), wafer B clearly exhibits fewer pore defects, which signifi-cantly diminishes the impact of ions and molecules in the air on the interior of the epitaxial layer. Consequently, parasitic leakage conduction through defective channels is mitigated, resulting in the elimination of output conduction for wafer A. The device exhibits an ON/OFF current ratio of ∼106 for wafer A and 107 for wafer B, with a low drain leakage current below 10 nA mm−1 and 1 nA mm−1 at a drain bias (VDS) of 0.5 V, respectively. The reduction of gate leakage to near noise levels further implies an improvement in the growth of the GaN channel.18) The threshold voltage (VTH), determined using the linear extrapolation method (i.e., the gate bias intercept of the linear extrapolation of the drain current at the peak transconductance point), is extracted to be approximately −19 V for wafer A and −13 V for wafer B. The lower drain leakage in the off-state at the gate-source bias VGS below the threshold voltage VTH for wafer B is consistent with the aforementioned output characteristics, indicating better channel quality achieved through layer subdivision, as shown in Fig. 4. As can be seen from Fig. 4(b), wafer B exhibits a steeper slope in the linear transfer curve on the right, indicating a lower defect density. The gate leakage is significantly reduced from wafer A to B with identical passivation, indicating fewer leakage paths through the gate dielectric, which is attributed to its superior surface morphology. The relatively high Ron in both wafers is attributed to the thin GaN channel thickness, which is directly on the AlN buffer forming the back barrier. Increasing the channel thickness and introducing a graded layer, along with further optimization of the growth process, will lead to a reduction in Ron.19)

The gate and source electrodes are biased at −30 V and 0 V, respectively, with the substrate left floating. The off-state characteristics are depicted in Fig. 5. Wafer A exhibits an IDSS leakage of ∼1 μA mm−1 at 1000 V, indicating a BV of around 1000 V. In contrast, Wafer B displays an IDSS leakage of about 1 μA mm−1 at 2500 V, suggesting a BV of ∼2500 V. The significant improvement in BV is speculated to result from the superior insulating properties of the GaN channel. The subdivi-sion of the GaN channel leads to fewer defect states and reduced pore defects, resulting in a high BV. Additionally, the character-istics of the IDSS reveal a sudden breakdown, which may be attributed to lateral failure of the device. This behavior suggests that the breakdown mechanism could be a punch-through of the channel layer, as the better channel quality of wafer B indicates a higher BV. A vertical breakdown is unlikely to occur because of the floating substrate and the insulating properties of the sapphire substrate, as indicated by the off-state IDSS characteristics.20) The high BV for wafer B is also believed to be due to a simplified peak electric field condition with a single field plate. In this scenario, only two electric field peaks at the field plate edge and the drain edge determine the BV and the peak electric field at the field plate edge is reduced below the breakdown strength of GaN.13,14) Consequently, this configuration allows our GaN HEMT with a single field plate to sustain a BV exceeding 2500 V at an IDSS leakage of 1 μA mm−1. Our previous work on MOCVD-grown GaN HEMTs with a single field plate structure has demonstrated a BV over 2400 V, supporting our speculation on the breakdown mechanisms.12) Table I summarizes the BV and leakage current characteristics of various 1200 V rated GaN power HEMTs. Our work is unique in employing a single field plate technique, demonstrating relatively high BV and low IDSS leakage.12,21,22) The implementation of a single field plate structure, using the simplest form of field plate, may help reduce the total fabrication cost while maintaining a high BV.

Fig. 5. The off-state leakage current IDSS for (a) wafer A and (b) wafer B, and (c) simulated electric field distribution for no field plate and single field plate structures.

The dynamic Ron characteristics for the GaN HEMT fabricated in this work were measured using the Agilent B1505 dynamic measurement system to evaluate the current Fig. 6. Dynamic Ron characteristics under various OFF-state stresses.

collapse effect. The measurement setup was as follows: the ON-state was characterized by VGS = 0 V and VDS = 1 V. In the OFF-state, VGS was fixed at −20 V, and the OFF-state stress time was 10 ms, with various VDS values applied ranging from 0 to 800 V. Dynamic Ron was measured 200 μs after switching from the OFF-state to the ON-state, which is the minimum switching time of the system.23) The dynamic Ron/static Ron value for the MBE-grown GaN HEMT in this work was evaluated to be approximately 46% at 600 V, which is relatively higher compared with our previous work, as shown in Fig. 6.24) Such a difference may be attributed to either electron trapping associated with dislocations in the MBE-grown buffer layer or suboptimal LPCVD passivation on the MBE-grown in situ SiN under VDS stress as high as 600 V. Further work will be conducted utilizing low-tem-perature PECVD passivation instead of high-temperature LPCVD to mitigate current collapse.12)

In conclusion, we demonstrated a GaN power HEMT with a BV exceeding 2500 V, grown by MBE on sapphire through the use of a subdivided GaN channel and an ultra-thin AlN buffer layer grown by MBE, as well as the implementation of a single gate field plate technique. We demonstrated that this technique leads to fewer defect states and reduced pore defects, resulting in a high BV. These advantages highlight the potential of PA-MBE-grown GaN power HEMTs for high-power electronic applications. The novelty of this work resides primarily in the epitaxial growth method, while Ref. 12 is based on a novel chip design and chip processing method. Future work will focus on reducing dislocations to demonstrate the breakdown properties of large devices and to decrease Ron by introducing graded layers and optimizing the top barrier, as well as increasing the channel thickness.

Fig. 6. Dynamic Ron characteristics under various OFF-state stresses.

Acknowledgments The authors gratefully acknowledge the support from the Jiangsu Provincial Department of Finance Project through Grant No. BE2023048 for this work.

REFERENCES

1) O. S. Koksaldi, J. Haller, H. Li, B. Romanczyk, M. Guidry, S. Wienecke, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. **39**, 1014 (2018).

2) G. Gupta, M. Kanamura, B. Swenson, D. Bisi, B. Romanczyk, and C. Neufeld, 2022, IEEE 34th Int. Symp. on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada.

3) Z. Cheng, X. Li, L. Chen, L. Wang, Z. Li, and X. Tang, IEEE Trans. Electron Devices **71**, 7689 (2024).

4) O. Çiçek and Y. Badali, IEEE Trans. Device Mater. Reliab. **24**, 275 (2024).

5) M. T. Alam, S. Mukhopadhyay, M. M. Haque, S. S. Pasayat, and C. Gupta, Appl. Phys. Express **18**, 016501 (2025).

6) K. Shinohara et al., 2010, Int. Electron Devices Meeting, San Francisco, CA, USA30.1.1.

7) Y. Yue et al., Jpn. J. Appl. Phys. **52**, 08JN14 (2013).

8) D. S. Lee et al., IEEE Electron Device Lett. **34**, 969 (2013).

9) W. Xing, Z. Liu, H. Qiu, G. I. Ng, and T. Palacios, IEEE Electron Device Lett. **38**, 619 (2017).

10) S. Bajaj, Z. Yang, F. Akyol, P. S. Park, Y. Zhang, A. L. Price, S. Krishnamoorthy, D. J. Meyer, and S. Rajan, IEEE Trans. Electron Devices **64**, 3114 (2017).

11) T. D. Moustakas, E. Iliopoulos, A. V. Sampath, H. M. Ng, D. Doppalapudi, M. Misra, D. Korakakis, and R. Singh, J. Cryst. Growth **227–228**, 13 (2001).

12) Z. Yang, Y. Liao, J. Zhuang, H. Dong, S. Zhang, L. Zhu, B. Zhang, G. Yu, Z. Zeng, and B. Zhang, IEEE Trans. Electron Devices under review (2025).

13) X. Li et al., IEEE Trans. Electron Devices **71**, 3989 (2024).

14) Z. C. Yang, Y. Q. Wang, J. G. Zhuang, and E. Liao, 2025, 15th Int. Conf. on Power, Energy, and Electrical Engineering (CPEEE), Fukuoka, Japan, 2025.

15) N. Sharma, S. K. Dhakad, C. Periasamy, and N. Chaturvedi, Mater. Sci. Semicond. Process. **87**, 195 (2018).

16) M. Piazza, C. Dua, M. Oualil, E. Morvan, D. Carsetti, and F. Wyczisk, Microelectron. Reliab. **49**, 1222 (2009).

17) A. H. Mohamed, N. A. B. Ghazali, H. M. H. Chong, R. J. Cobley, L. Li, and K. Kaina, Solid-State Electron. **172**, 107867 (2020).

18) S. Shin et al., APL Electronic Devices **1**, 036120 (2025).

19) K. Harrouche, S. Venkatachalam, F. Grandpierre, E. Okada, and F. Medjdoub, Appl. Phys. Express **15**, 116504 (2022).

20) S. Wienecke et al., 2025 IEEE Int. Reliability Physics Symp. (IRPS), Monterey, CA, USA3A.1-1, 2025.

21) S. Li, Y. Ma, W. Lu, M. Li, L. Wang, Z. Zhang, T. Zhu, and Y. Li, Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA1, 2023.

22) A. Li, F. Li, W. Wang, Y. Zhu, W. Liu, G. H. Yu, Z. Zeng, and B. Zhang, Proc. of The 2024 36TH Int. Symp. on Power Semiconductor Devices and ICs (ISPSD) 2-6, Bremen, Germany, 2024.

23) R. Hao et al., IEEE Electron Device Lett. **38**, 1567 (2017).

24) M. Cioni et al., Microelectron. Reliab. **168**, 115666 (2025).

1) O. S. Koksaldi, J. Haller, H. Li, B. Romanczyk, M. Guidry, S. Wienecke, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. **39**, 1014 (2018).

2) G. Gupta, M. Kanamura, B. Swenson, D. Bisi, B. Romanczyk, and C. Neufeld, 2022, IEEE 34th Int. Symp. on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada.

3) Z. Cheng, X. Li, L. Chen, L. Wang, Z. Li, and X. Tang, IEEE Trans. Electron Devices **71**, 7689 (2024).

4) O. Çiçek and Y. Badali, IEEE Trans. Device Mater. Reliab. **24**, 275 (2024).

5) M. T. Alam, S. Mukhopadhyay, M. M. Haque, S. S. Pasayat, and C. Gupta, Appl. Phys. Express **18**, 016501 (2025).

6) K. Shinohara et al., 2010, Int. Electron Devices Meeting, San Francisco, CA, USA30.1.1.

7) Y. Yue et al., Jpn. J. Appl. Phys. **52**, 08JN14 (2013).

8) D. S. Lee et al., IEEE Electron Device Lett. **34**, 969 (2013).

9) W. Xing, Z. Liu, H. Qiu, G. I. Ng, and T. Palacios, IEEE Electron Device Lett. **38**, 619 (2017).

10) S. Bajaj, Z. Yang, F. Akyol, P. S. Park, Y. Zhang, A. L. Price, S. Krishnamoorthy, D. J. Meyer, and S. Rajan, IEEE Trans. Electron Devices **64**, 3114 (2017).

11) T. D. Moustakas, E. Iliopoulos, A. V. Sampath, H. M. Ng, D. Doppalapudi, M. Misra, D. Korakakis, and R. Singh, J. Cryst. Growth **227–228**, 13 (2001).

12) Z. Yang, Y. Liao, J. Zhuang, H. Dong, S. Zhang, L. Zhu, B. Zhang, G. Yu, Z. Zeng, and B. Zhang, IEEE Trans. Electron Devices under review (2025).

13) X. Li et al., IEEE Trans. Electron Devices **71**, 3989 (2024).

14) Z. C. Yang, Y. Q. Wang, J. G. Zhuang, and E. Liao, 2025, 15th Int. Conf. on Power, Energy, and Electrical Engineering (CPEEE), Fukuoka, Japan, 2025.

15) N. Sharma, S. K. Dhakad, C. Periasamy, and N. Chaturvedi, Mater. Sci. Semicond. Process. **87**, 195 (2018).

16) M. Piazza, C. Dua, M. Oualil, E. Morvan, D. Carsetti, and F. Wyczisk, Microelectron. Reliab. **49**, 1222 (2009).

17) A. H. Mohamed, N. A. B. Ghazali, H. M. H. Chong, R. J. Cobley, L. Li, and K. Kaina, Solid-State Electron. **172**, 107867 (2020).

18) S. Shin et al., APL Electronic Devices **1**, 036120 (2025).

19) K. Harrouche, S. Venkatachalam, F. Grandpierre, E. Okada, and F. Medjdoub, Appl. Phys. Express **15**, 116504 (2022).

20) S. Wienecke et al., 2025 IEEE Int. Reliability Physics Symp. (IRPS), Monterey, CA, USA3A.1-1, 2025.

21) S. Li, Y. Ma, W. Lu, M. Li, L. Wang, Z. Zhang, T. Zhu, and Y. Li, Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA1, 2023.

22) A. Li, F. Li, W. Wang, Y. Zhu, W. Liu, G. H. Yu, Z. Zeng, and B. Zhang, Proc. of The 2024 36TH Int. Symp. on Power Semiconductor Devices and ICs (ISPSD) 2-6, Bremen, Germany, 2024.

23) R. Hao et al., IEEE Electron Device Lett. **38**, 1567 (2017).

24) M. Cioni et al., Microelectron. Reliab. **168**, 115666 (2025).

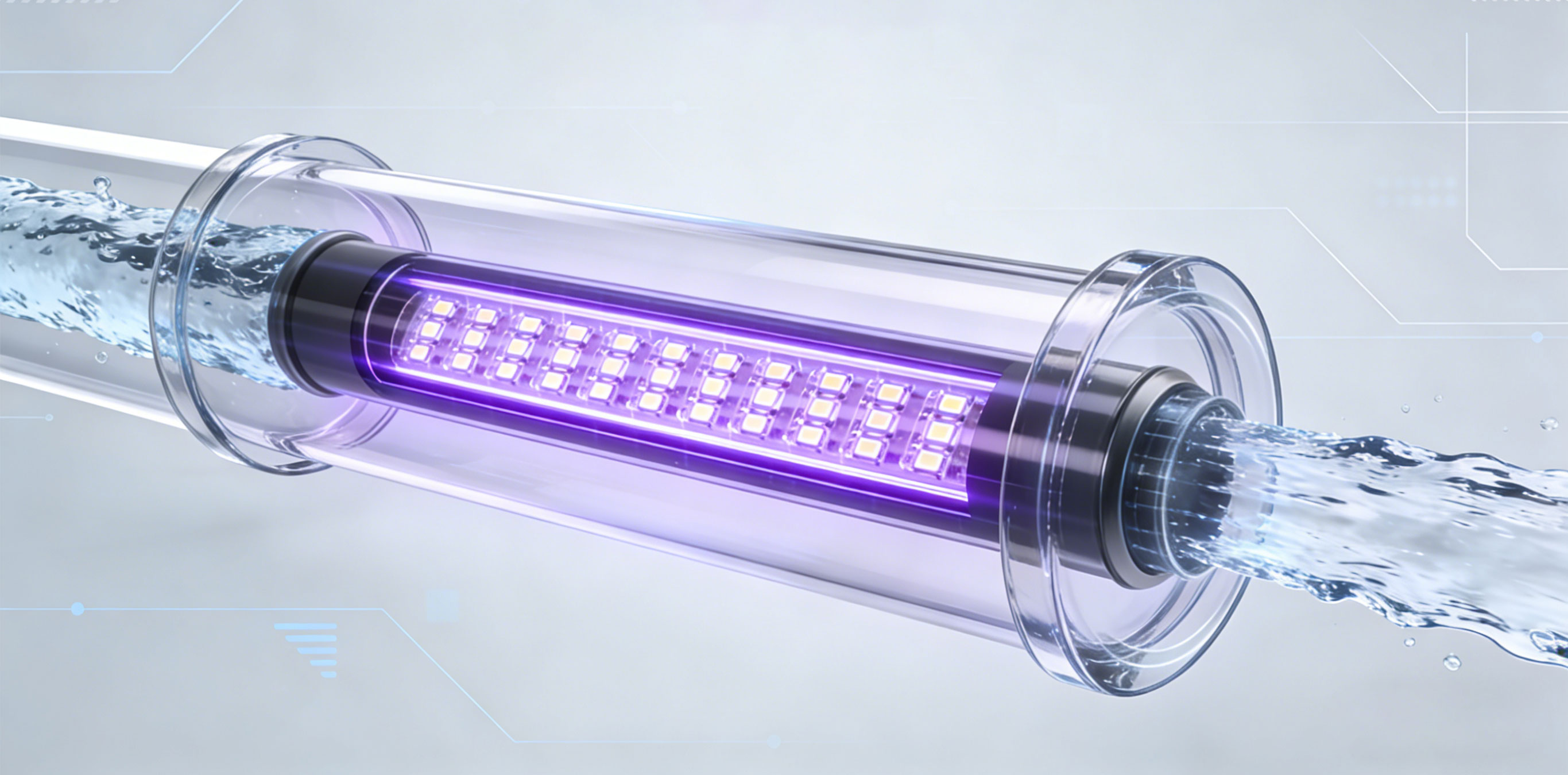

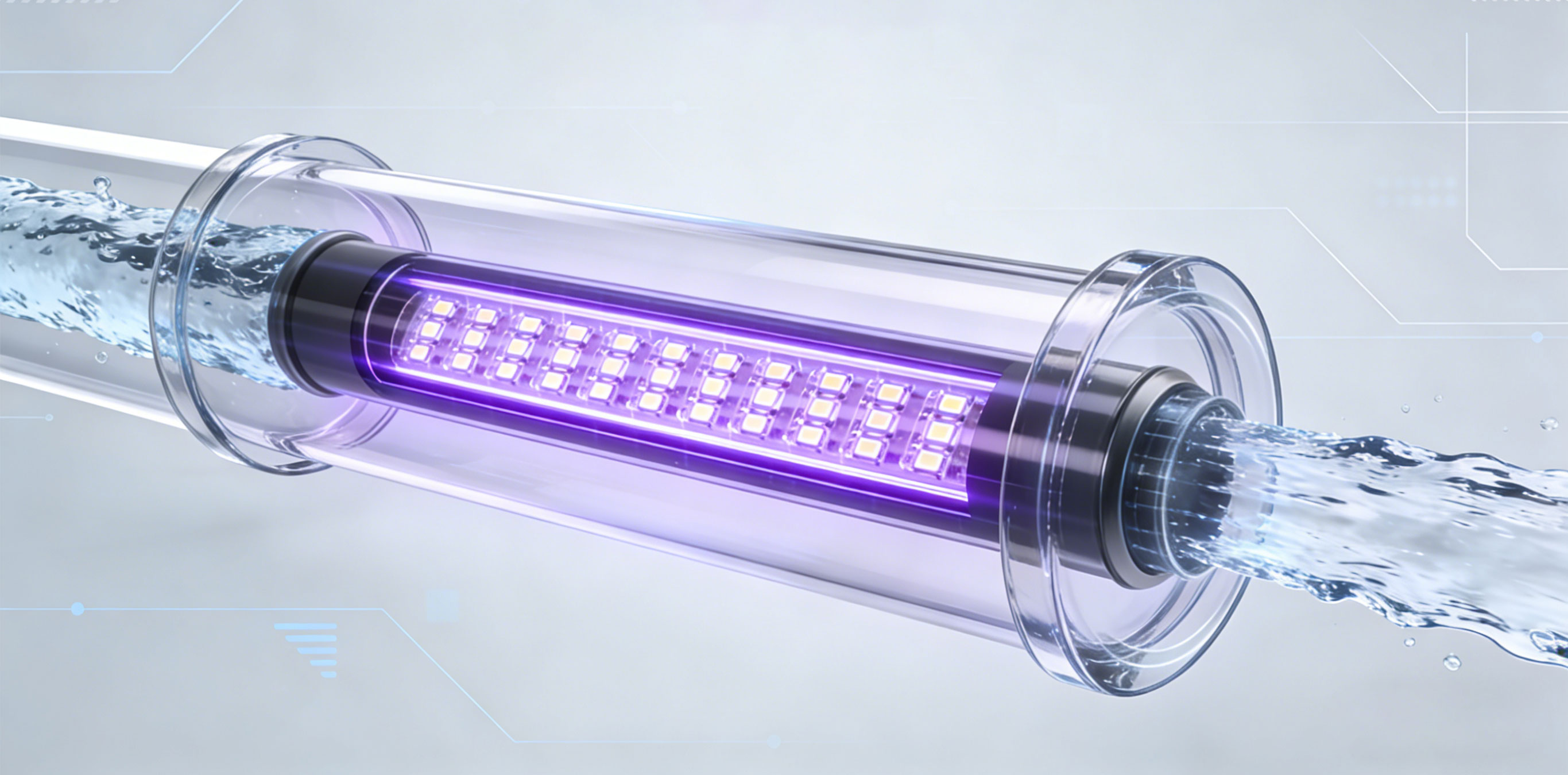

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers.

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers. Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit

Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment.

UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment. UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.

UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.