Single-field-plate GaN HEMTs achieving >2400 V breakdown voltage and

106% dynamic on-resistance at 600 V stress

Zhichao Yang¹①, Eason Liao¹, Junqang Zhuang¹, Hao Dong¹, Shuangshuang Zhang¹, Lei Zhu¹, Zezheng Yang¹, Bingliang Zhang², Guohao Yu³, Zhongming Zeng³, and Baoshun Zhang³

¹MASSPHOTON LIMITED, Hong Kong SAR, People's Republic of China

²Suzhou Powerhouse Electronics Technology Co., Ltd, Suzhou, Jiangsu 215123, People's Republic of China

³Nanofabrication facility, Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Suzhou, Jiangsu 215123, People's Republic of China

*E-mail: zcy@massphoton.com; eason@massphoton.com

Main text

Figures

Tables

References

This work reports GaN power high-electron-mobility transistors (HEMTs) that achieve a breakdown voltage (BV) exceeding 2400 V (defined IDSS <1 μA mm-¹)) through the implementation of a single gate field plate (FP). This design establishes a simplified yet optimized electric field profile, which is key to achieving a high BV while maintaining favorable dynamic performance. The dynamic ON-resistance (Ron) remains as low as 106% after OFF-state VDS stress at 600 V. The combination of high BV and robust dynamic characteristics demonstrates that the single gate FP technique is a promising approach for the mass production of high-performance GaN power HEMTs, offering the potential for reduced process complexity and cost without compromising device performance. © 2026 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

Fig. 1. (a) Schematic of the cross-section of a GaN HEMT with a single field plate (b) microscopic image of the 2 inch wafer post-process completion (c) microscopic image of the fabricated GaN HEMT with a single field plate (d) focused ion beam (FIB) image of the fabricated GaN HEMT with a single field plate.

Fig. 2. Key process nodes of the GaN HEMT with a single field plate.

Fig. 3. SEM image of the GaN HEMT passivated with (a) ICPCVD (wafer A) and (b) PECVD.

Fig. 4. Output characteristics of the GaN HEMT.

3.1. Static breakdown characteristics and mechanisms via electric field simulation

Figure 5 depicts the OFF-state breakdown characteristics of the fabricated GaN HEMTs. A bias voltage of −15 V was applied to the gate, 0 V to the source, and the substrate was left floating. Wafer A, featuring ICPCVD SiN passivation, exhibits a BV higher than 2000 V for 44% of its devices. In contrast, wafer B with PECVD SiN passivation shows that nearly 70% of its devices have a BV exceeding 2400 V. The OFF-state leakage current IDSS is approximately 20 μA for wafer A and 1 μA for wafer B at a drain-source voltage VDS of 2000 V, as illustrated in Figs. 5(c) and 5(e), respectively. The marked reduction in IDSS leakage for wafer B compared to wafer A is attributed to superior passivation of surface defects under the higher deposition temperature of PECVD (350 °C), as suggested by the SEM images in Fig. 3. The substantial improvement in BV uniformity and IDSS leakage for wafer B (PECVD at 350 °C) over wafer A (ICPCVD at 250 °C) underscores the critical role of deposition tempera-ture. Higher temperature promotes better interface repair, film stoichiometry, and hydrogen redistribution, all of which enhance dielectric robustness and interface quality. For both wafers, IDSS increases rapidly after a high voltage beyond 2000 or 2400 V, indicating that the breakdown is caused by a vertical failure mode which occurs beyond the lateral failure mode that happens between the gate and drain electrodes.25) The single-FP applied in our work extends the lateral failure mode and postpones the vertical failure mode compared to multiple-FP, and thus can increase BV, as indicated by the comparison between our work and reference,19) which has the same buffer structure. Table I summarizes the blocking capabilities of various 1200 V rated GaN power HEMTs. Benchmarking against state-of-the-art multiple-FP designs in Table I reveals that our single-FP device achieves a superior BV while maintaining exceptionally low IDSS leakage. This demonstrates that careful single-FP optimization can match the static performance of more complex architectures. The physics is further explained with the Silvaco simulation results in Fig. 6(b). From Fig. 6(a), the IDSS leakage is reduced at the same VDS bias as the gate FP dielectric thickness increases from 150 nm to 300 nm. This is accom-panied by the reduction in the electric field peak at the gate FP edge, as shown in Fig. 6(b). Once the electric field peak at the drain edge exceeds the breakdown strength of the GaN material, the IDSS leakage is no longer reduced. The relatively low IDSS leakage in our work as compared to the reference works is attributed to the simplified electric field peak condition indicated from the Silvaco simulation, as fewer weak points would be present when the number of electric field peaks is reduced.26) In the GaN-on-Si epitaxial structure of this work, the highly resistive carbon-doped buffer layer and the conductive silicon substrate jointly govern the vertical breakdown path. At extremely high drain bias (>2000 V), the vertical electric field promotes electron injection from the substrate into the buffer. These electrons are captured by deep-level traps, forming space charge that distorts the field distribution and leads to localized Joule heating, eventually triggering thermal runaway and the transition to the vertical failure mode. The achievement of >2400 V BV on a conductive Si substrate demonstrates the effectiveness of the single-FP design in managing the lateral field and postponing vertical breakdown. This potential highlights its suitability for more demanding applications, such as 1200 V and higher-voltage power markets where insulating substrates are typically employed.11,17)

3.2. Thermal dissipation analysis

At high switching frequencies (e.g. >100 kHz), reduced cooling time between cycles will lead to an elevated average channel temperature. This may affect dynamic Ron through two primary physical pathways: (i) increased emission rates from existing traps, which could partially recover collapse; and (ii) possible activation of deeper traps or enhanced interface state generation under cyclic thermo-mechanical stress, which may ultimately degrade high-frequency perfor-mance. Despite the complexity of real operating conditions, our single-FP design offers inherent thermal advantages: our device exhibits uniform interfaces between semiconductor and passivation/dielectric layers (Fig. 1) and excellent planarity (Fig. 3), both of which are crucial for efficient vertical heat conduction from the channel toward the substrate. In contrast, multiple-layer, non-planar structures with multiple-FP can introduce thermal bottlenecks at a) BV is normalized by LGD.

topographic steps. Therefore, our simplified single-FP archi-tecture is favorable for/offers inherent advantages for thermal management.

[1] W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, and T. S. Ogura, “Design and demonstration of high breakdown voltage GaN high electron mobility transistor (HEMT) using field plate structure for power electronics applications,” Jpn. J. Appl. Phys. 43, 2239 (2004).

[2] K. Shinohara et al., “220GHz fT and 400GHz fmax in 40-nm GaN DH-HEMTs with re-grown ohmic,” Int. Electron Devices Meeting, San Francisco, CA, USA, 2010 p. 30.1.1.

[3] U. Singisetti, M. H. Wong, S. Dasgupta, J. S. Speck, and U. K. Mishra, “Enhancement-mode N-polar GaN metal-insulator-semiconductor field effect transistors with current gain cutoff frequency of 120 GHz,” Appl. Phys. Express 4, 024103 (2011).

[4] Y. Yue et al., “Ultrascaled InAlN/GaN high electron mobility transistors with cutoff frequency of 400 GHz,” Jpn. J. Appl. Phys. 52, 08JN14 (2013).

[5] M. H. Wong et al., “N-polar GaN epitaxy and high electron mobility transistors,” Semicond. Sci. Technol. 28, 074009 (2013).

[6] O. S. Koksaldi, J. Haller, H. Li, B. Romanczyk, M. Guidry, S. Wienecke, S. Keller, and U. K. Mishra, “N-polar GaN HEMTs exhibiting record breakdown voltage over 2000 V and low dynamic on-resistance,” IEEE Electron Device Lett. 39, 1014 (2018).

[7] Y. Zhang, M. Sun, J. Perozek, Z. Liu, A. Zubair, D. Piedra, N. Chowdhury, X. Gao, K. Shepard, and T. Palacios, “Large-area 1.2 kV GaN vertical power FinFETs with a record switching figure of merit,” IEEE Electron Device Lett. 40, 75 (2025).

[8] P. Shrestha et al., “High linearity and high gain performance of N-polar GaN MIS-HEMT at 30 GHz,” IEEE Electron Device Lett. 41, 681 (2020).

[9] S. H. Sohel et al., “Linearity improvement with AlGaN polarization-graded field effect transistors with low pressure chemical vapor deposition grown SiNx passivation,” IEEE Electron Device Lett. 41, 19 (2020).

[10] J.-S. Moon et al., “Power scaling of graded-channel GaN HEMTs with mini-field-plate T-gate and 156 GHz fT,” IEEE Electron Device Lett. 42, 796 (2021).

[11] G. Gupta et al., “1200V GaN switches on sapphire substrate,” IEEE 34th Int. Symp. on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada, 2025.

[12] Z. Cheng, X. Li, L. Chen, L. Wang, Z. Li, and X. Tang, “Achieving ≥ 1200 V high-performance GaN HEMTs on sapphire with carbon-doped buffer,” IEEE Trans. Electron Devices 71, 7689 (2024).

[13] O. Çiçek and Y. Badali, “A review: breakdown voltage enhancement of GaN semiconductors-based high electron mobility transistors,” IEEE Trans. Device Mater. Reliab. 24, 275 (2024).

[14] M. T. Alam, S. Mukhopadhyay, M. M. Haque, S. S. Pasayat, and C. Gupta, “3 kV monolithic bidirectional GaN HEMT on sapphire,” Appl. Phys. Express 18, 016501 (2025).

[15] H. Li et al., “GaN-on-Si HEMT for D-band power amplification demonstrating 0.67 W/mm at 10 V,” IEEE Electron Device Lett. 46, 1749 (2025).

[16] S. Luo, F. Wang, and K. Zhang, “Improved breakdown voltage and Vth stability in hybrid gate p-GaN power HEMTs on sapphire substrate,” Jpn. J. Appl. Phys. 65, 024002 (2025).

[17] S. Li et al., “1200 V E-mode GaN monolithic integration platform on sapphire with ultra-thin buffer technology,” Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023.

[18] X. Li et al., “Demonstration of > 8 kV GaN HEMTs with CMOS-compatible manufacturing on 6-in sapphire substrates for medium-voltage applications,” IEEE Trans. Electron Devices 71, 3989 (2024).

[19] W. Wang (Member, IEEE) et al., “Suppression of dynamic resistance degradation in 1200 V GaN-on-Sapphire E-Mode GaN HEMTs by drain-side thin p-GaN design,” IEEE Trans. Electron Devices 72, 1537 (2025).

[20] N. Sun et al., “6 in. high-voltage GaN-based E-mode HEMTs with ultrathin barrier structures: interface quality and its reliability,” Appl. Phys. Lett. 126, 112105 (2025).

[21] J. Li, R. Zhu, K. M. Wong, and K. M. Lau, “Fully-vertical GaN-on-SiC trench MOSFETs,” IEEE Electron Device Lett. 46, 282 (2025).

[22] R. Hao et al., “Breakdown enhancement and current collapse suppression by high-resistivity GaN Cap layer in normally-off AlGaN/GaN HEMTs,” IEEE Electron Device Lett. 38, 1567 (2017).

[23] Y.-K. Lin, J. Bergsten, H. Leong, A. Malmros, J.-T. Chen, D.-Y. Chen, O. Kordina, H. Zirath, E. Y. Chang, and N. Rorsman, “A versatile low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs,” Semicond. Sci. Technol. 33, 095019 (2018).

[24] Z. Tang, Q. Jiang, Y. Lu, S. Huang, S. Yang, X. Tang, and K. J. Chen, “600 V normally off SiNx /AlGaN/GaN MIS-HEMT with large gate swing and low current collapse,” IEEE Electron Device Lett. 34, 1373 (2013).

[25] S. Wienecke et al., “3 factor accelerated lifetime testing in lateral GaN power HEMTs: a tutorial,” 2025 IEEE Int. Reliability Physics Symp. (IRPS), Monterey, CA, USA, 2025, p. 3A.1–1.

[26] M. J. Uren, M. Caesar, S. Karboyan, P. Moens, P. Vanmeerbeek, and M. Kuball, “Electric field reduction in C-doped AlGaN/GaN on Si high electron mobility transistors,” IEEE Electron Device Lett. 36, 826 (2015).

[27] P. Moens et al., “On the impact of carbon-doping on the dynamic Ron and off-state leakage current of 650 V GaN power devices,” Proc. of the 27th Int. Symp. on Power Semiconductor Devices & IC’s, Kowloon Shangri-La, Hong Kong, 2015.

[28] M. Cioni et al., “Effect of 2DEG density and drain/source field plate design on dynamic-RON of 650 V AlGaN/GaN HEMTs,” Microelectron. Reliab. 168, 115666 (2025).

[29] M. Hua, C. Liu, S. Yang, S. Liu, Y. Lu, K. Fu, Z. Dong, Y. Cai, B. Zhang, and K. J. Chen, “650-V GaN-based MIS-HEMTs using LPCVD-SiNx as passivation and gate dielectric, 2015, IEEE 27th Int. Symp. on Power Semiconductor Devices and IC’s, ISPSD, 2015.

Get in Touch

Recent Posts

-

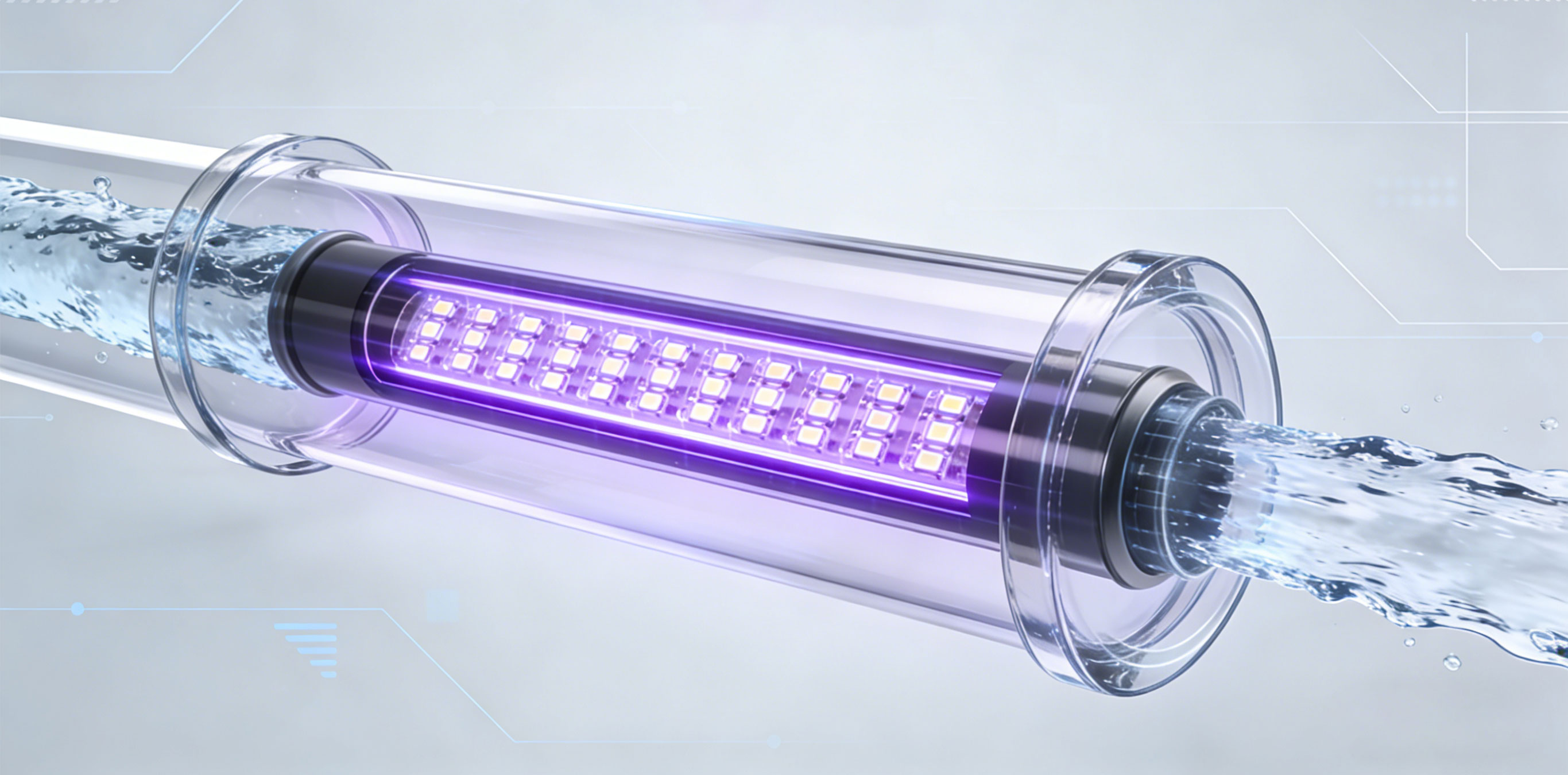

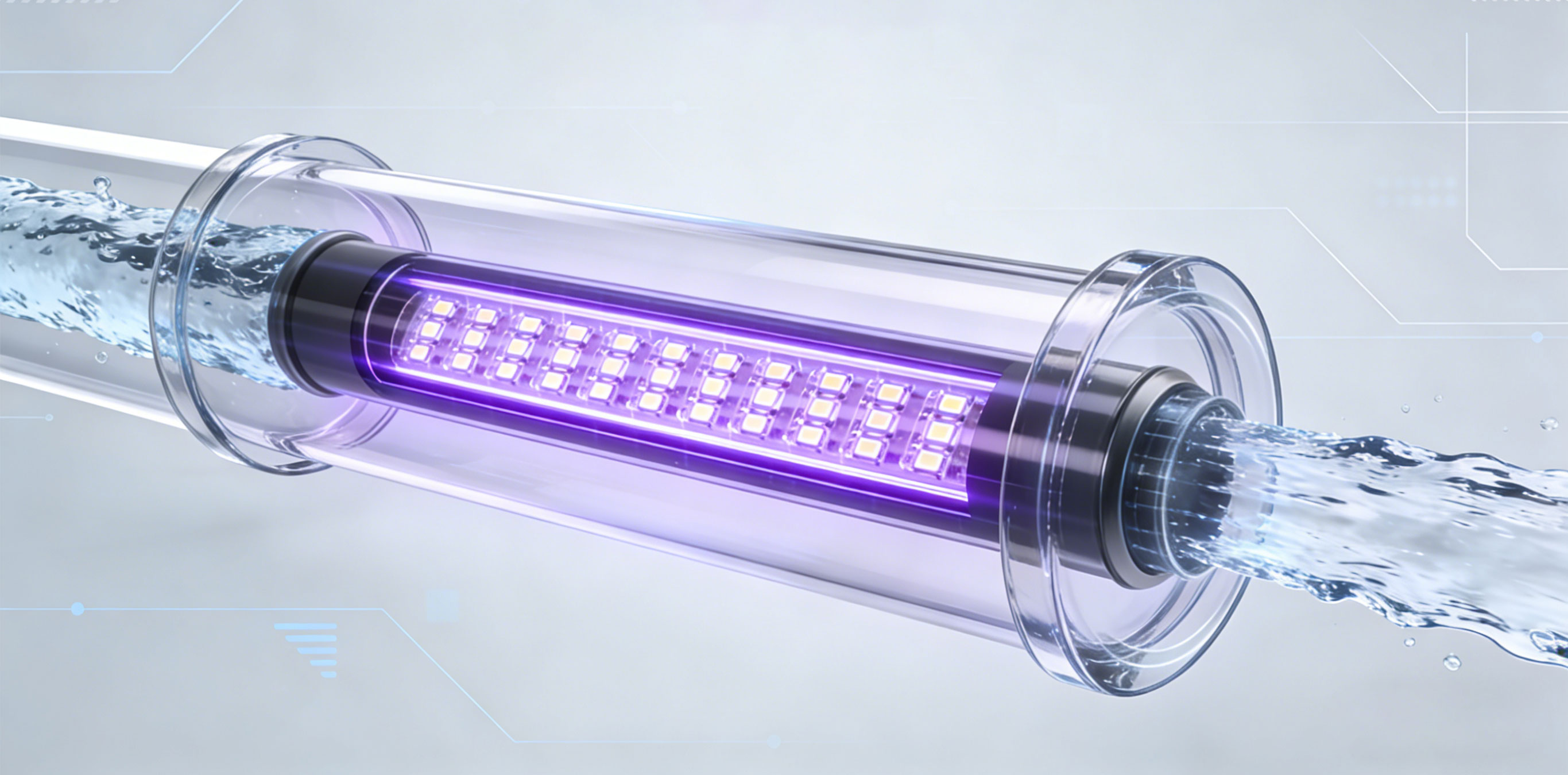

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers.

The article introduces UVC LED as a revolutionary, mercury-free, energy-efficient alternative to traditional mercury lamps and chlorination for disinfecting reused agricultural water in greenhouses, aquaculture, and field irrigation. It highlights benefits like 99.999% pathogen kill rates, 30-50% water/fertilizer savings, reduced maintenance, and compliance with green standards, with practical selection tips for farmers. -

Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit

Since ultraviolet light was first used for drinking water disinfection in 1910, this technology has been widely applied in the food and beverage industry. UVC ultraviolet light (wavelength 200–280 nm) can effectively inactivate microorganisms such as bacteria, viruses, fungi, algae, and protozoa wit -

UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment.

UV disinfection uses short‑wavelength UV‑C light to penetrate microorganisms in water and damage their DNA or RNA, so they can no longer reproduce or cause infection. This purely physical process adds no chemicals and does not change the taste, odor, or mineral content of the water, making it widely used for drinking and industrial water treatment. -

UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.

UV‑C LED disinfection is transforming large‑scale water treatment by providing a mercury‑free, energy‑efficient, and long‑lasting alternative to traditional mercury lamps. Its precise 265–280 nm emission enables rapid microbial inactivation without producing harmful by‑products, aligning perfectly with modern sustainability and safety goals for municipal and industrial water systems.